So với các tín hiệu thô thu trực tiếp từ cảm biến môi trường, dữ liệu đã qua xử lý của chip Analog Front-end (AFE) ít nhiễu và có biên độ lớn hơn nên có thể quan sát trên máy hiển thị sóng.

Vượt qua 39 hồ sơ, dự án “Thiết kế chip Analog Front-end nhiễu thấp tái cấu hình ứng dụng thu nhận tín hiệu từ cảm biến trên công nghệ CMOS 180nm” của Phạm Thế Hùng - học viên cao học Khoa Điện tử - Viễn thông, Trường ĐH Khoa học Tự nhiên ĐHQG-HCM, đã đoạt giải Nhất Cuộc thi Thiết kế vi mạch cho đô thị thông minh lần I, do Khu Công nghệ cao TP.HCM tổ chức.

Loại bỏ nhiễu và khuếch đại tín hiệu

Ban đầu, Thế Hùng thiết kế chip AFE nhằm tăng khả năng thu nhận tín hiệu điện não EEG từ cảm biến thô. Nguyên nhân là việc quan sát tín hiệu điện não thu trực tiếp từ cảm biến rất khó khăn do tín hiệu này có biên độ, tần số khá thấp và bị ảnh hưởng bởi nhiều nguồn nhiễu khác nhau.

Hùng giải thích: “Chip AFE của mình có khả năng loại bỏ nhiễu tần số thấp và khuếch đại tín hiệu điện não thu được từ cảm biến. Do đó, bác sĩ có thể quan sát tín hiệu điện não trực tiếp trên máy hiển thị sóng một cách rõ ràng”.

Đây cũng là đề tài luận văn tốt nghiệp đạt 10 điểm, được Hùng thực hiện từ cuối năm 2022 đến tháng 10/2023. Theo nam sinh, hội đồng đánh giá cao đề tài của cậu vì đã thiết kế được các mạch điện theo quy trình thiết kế vi mạch tương tự, trong khi thông thường, sinh viên chỉ dừng lại ở bước mô phỏng trên phần mềm. Hùng cũng nhận được góp ý về việc giảm kích thước mạch điện, nâng cao trở kháng ngõ vào và giảm hệ số nhiễu để cải thiện hiệu suất mạch điện.

Hai tháng sau, Thế Hùng biết đến Cuộc thi Thiết kế vi mạch cho đô thị thông minh lần I. Dù chỉ còn 2 tháng để gửi hồ sơ nhưng nam sinh vẫn quyết định cải tiến sản phẩm, đồng thời bổ sung tính năng thu nhận tín hiệu từ cảm biến môi trường cho chip AFE.

Theo Hùng, vì xử lý loại tín hiệu khác nên cấu trúc mạch điện của chip AFE cũng thay đổi. Do đó, ngoài việc giảm kích thước mạch, cải thiện hệ số nhiễu và trở kháng ngõ vào, nam sinh còn thiết kế thêm mạch Reconfigurable Acquisition Circuit (RAC) để chip AFE có thể thu nhận tín hiệu từ cảm biến môi trường.

Để chọn được mạch điện này, Thế Hùng đã phải thử nghiệm nhiều loại mạch khác nhau, mỗi lần tốn khoảng 3-4 tuần. Khi kết quả không như mong đợi, cậu phải tìm kiếm các mạch điện khác nên mất khá nhiều thời gian. Đến khi mạch RAC mang lại kết quả tốt nhất, Hùng mới hoàn thiện sơ đồ nguyên lý và thực hiện mô phỏng trên phần mềm, tiếp đến là thiết kế vật lý, kiểm tra vật lý (DRC/LVS) và mô phỏng sau layout cho toàn bộ chip AFE.

“Dù phải hiệu chỉnh liên tục đến tận vòng chung kết mới hoàn thành nhưng mình vẫn rất vui vì chip AFE có tính năng đa dạng hơn, phù hợp hơn với yêu cầu của ban tổ chức” - Thế Hùng bày tỏ.

Sẽ phát triển thành lõi IP

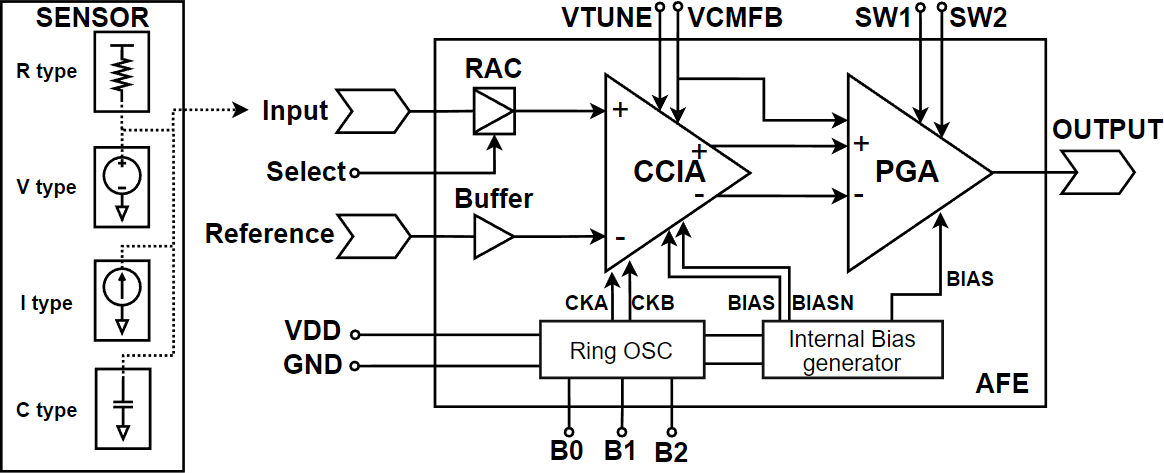

Theo Thế Hùng, sau khi được cải tiến, chip AFE có dạng hình chữ nhật với kích thước 516,9 x 670,72 (micrômét). Về cấu trúc, chip có 3 khối chính là RAC, Capacitively Coupled Chopper Instrumentation Amplifier (CCIA) và Programmable Gain Amplifier (PGA).

Mạch RAC có vai trò thu một trong 4 loại tín hiệu từ môi trường (điện áp, dòng điện, điện dung, điện trở) thông qua cảm biến và chuyển đổi thành tín hiệu dạng điện áp để dễ dàng xử lý hơn. Tín hiệu này sẽ đi qua khối CCIA để giảm nhiễu tần số thấp và được khuếch đại nhờ khối PGA. Kết quả là chip AFE cung cấp tín hiệu tương tự ít nhiễu và có biên độ lớn hơn nhiều lần so với tín hiệu thô ban đầu.

Chip AFE có thể xử lý 4 loại tín hiệu từ môi trường, trong khi các sản phẩm trên thị trường thường chỉ xử lý tín hiệu điện áp. Người dùng còn có thể điều chỉnh hệ số khuếch đại của chip AFE với giá tri ngõ ra khác nhau sao cho phù hợp với từng loại cảm biến để thu được tín hiệu tốt nhất.

Hiện tại, chip AFE có thể được ứng dụng cho các hệ thống thu nhận dữ liệu từ cảm biến môi trường hoặc y sinh, chẳng hạn các tín hiệu ánh sáng, nhiệt độ, độ ẩm, CO2 hoặc điện não .

Thế Hùng chia sẻ: “Các tín hiệu thu được từ chip AFE sẽ hỗ trợ rất lớn cho việc lưu trữ và phân tích dữ liệu trong hệ thống Internet of Things (IoT), Artificial Intelligence of Things (AIoT) và các thiết bị biên (Edge devices). Ví dụ, các mạch trong chip AFE hiện tại có thể kết hợp các mạch chuyển đổi tương tự sang số (ADC) hay vi điều khiển (MCU) để phân tích và tính toán dữ liệu”.

Khi biết tin dự án đoạt giải Nhất cuộc thi Thiết kế vi mạch cho đô thị thông minh lần I, Thế Hùng cảm thấy rất vui vì giải thưởng đã chứng minh năng lực của cậu trong lĩnh vực thiết kế vi mạch. Đây cũng là cơ hội để cậu có thêm góc nhìn thực tế và định hướng cải tiến sản phẩm.

“Đề tài của mình được nhiều người quan tâm và đánh giá là hoàn thành yêu cầu của cuộc thi, nhưng còn hạn chế là chi phí sản xuất khá cao, một số kỹ thuật mà mình áp dụng chưa phù hợp. Trong tương lai, mình sẽ tiếp tục cải tiến sản phẩm để có thể áp dụng vào thực tế” - Thế Hùng bộc bạch.

Là giảng viên hướng dẫn của Thế Hùng, TS Lê Đức Hùng - Trưởng Bộ môn Điện tử, Khoa Điện tử - Viễn thông, nhận xét chip AFE được đề xuất sẽ góp phần giảm thời gian thiết kế, giá thành, tối ưu hóa kích thước và năng lượng tiêu hao cho các hệ thống thu nhận dữ liệu.

TS Hùng cho biết: “Sắp tới, chip AFE sẽ tiếp tục được phát triển để có kích thước nhỏ hơn, thu nhận tín hiệu với tần số cao hơn và đánh giá kỹ hơn với thông số PVT (Process, voltage, temperature). Lõi AFE sẽ được đúc thành chip thành phẩm trên một công nghệ CMOS cụ thể và được phát triển trên các công nghệ khác nhau để hình thành lõi sở hữu trí tuệ bán dẫn (IP) có thể thương mại hóa, góp phần đa dạng hóa hệ sinh thái vi mạch bán dẫn trong nước”.

|

Hướng tới chuyển giao công nghệ sản xuất Cuộc thi Thiết kế vi mạch cho đô thị thông minh được Khu Công nghệ cao TP.HCM chủ trì, phối hợp Thành đoàn TP.HCM, Sở Thông tin và Truyền thông, Sở Khoa học và Công nghệ TP.HCM, ĐHQG-HCM tổ chức thường niên, nhằm tìm kiếm các sản phẩm, ý tưởng thiết kế vi mạch trong bối cảnh TP.HCM tập trung đầu tư phát triển, đẩy mạnh xây dựng đô thị thông minh. Cuộc thi dành cho sinh viên, học viên tại các trường đại học, cao đẳng, học viện trên toàn quốc. Những dự án đoạt giải cao sẽ được Khu Công nghệ cao TP.HCM hỗ trợ ươm tạo, hướng tới chuyển giao công nghệ sản xuất. |

THU TRANG

Hãy là người bình luận đầu tiên